Vhdl Program For Parity Generator

Your subscription to Autodesk software includes rights to install and activate your software on more than one computer. When a stand-alone Autodesk product is installed for the first time on a computer, the license must be activated for it to work beyond its trial period. If you have a perpetual license, reactivation is required when the previous activation of the product is somehow invalidated on the computer on which it is installed. Note for Subscription Customers: License transfer from one computer to another is not required to activate your subscription software on a new computer. Autodesk activation help. For each computer you wish to use, follow the standard for your software.

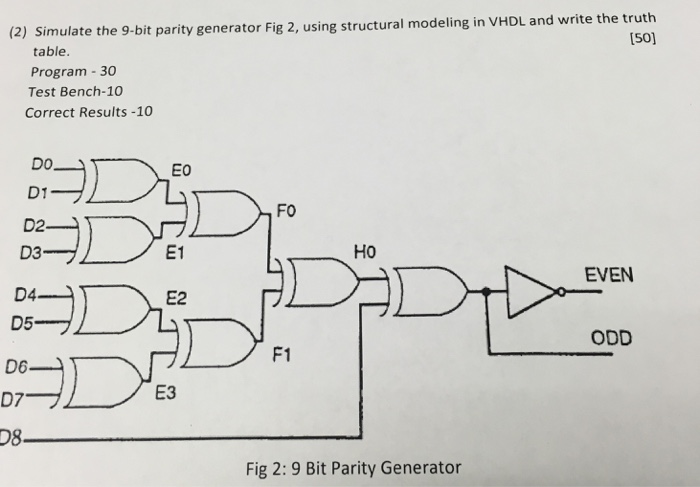

Apr 15, 2013 - VHDL IMPLEMENTATION OF PARITY GENERATOR USING STRUCTURAL STYLE OF MODELLING. Download game onet pokemon. -- program of 2 input xor gate.

>Anybody know how to code a parity generator in VHDL? Let's say for example a > >4-bit generator? Or some other even-bit generator? > Use the following function from package std_logic_misc: function XOR_REDUCE(ARG: STD_LOGIC_VECTOR) return UX01; ---------------------------------------------------------- -- Ben Cohen, Raytheon Systems, (310) 334-7389 -- ** 'VHDL Coding Styles and Methodologies, 2nd Edition', Ben Cohen, -- ISBN 0-7923-8474-1 Kluwer Academic Publishers, 1999 -- ** 'VHDL Answers to Frequently Asked Questions, 2nd Edition', -- Ben Cohen, ISBN 0-7923-8115-7 Kluwer Academic Publishers, 1998 -- Web page: Em 3/3/1999, 0:00 น. Wrote: > Anybody know how to code a parity generator in VHDL?

Let's say for example a > 4-bit generator? Or some other even-bit generator? > > Any help would be great. > > Thanks, > > -Steven > > ** you can send replies to this newgroup or to sbutts @ Two alternative descriptions: - one uses the well known parity chain. An alternative to this description is a process that contains a FOR LOOP with the XOR operation.

- the second has a more behavioural view, it count the numbers of ones. Both result in the same logic (witjh my synthesis tool) Regards, Egbert Molenkamp ENTITY parity1 IS GENERIC (nbits: positive:= 3); PORT (d: IN bit_vector(nbits-1 DOWNTO 0); odd: OUT bit; even: OUT bit); END parity1; ARCHITECTURE xor_chain OF parity1 IS SIGNAL chain: bit_vector (nbits DOWNTO 0); BEGIN chain(nbits). Be careful of using a loop or function call. You do not know how it will synthesize.

It may not matter as what you get may be fast enough. I tend to build my own parity function using parenthases to specify how I want the XOR gates structured. This way, I am more likely to get a balanced tree rather than a long chain: Good: ODD_PARITY. Wrote: > > Be careful of using a loop or function call. You do not know how it will > synthesize. It may not matter as what you get may be fast enough. I tend to > build my own parity function using parenthases to specify how I want the XOR > gates structured.

This way, I am more likely to get a balanced tree rather > than a long chain: > > Good: > ODD_PARITY > Not so good: > ODD_PARITY > BTW, to get even parity, just add one, better yet, ODD_PARITY = EVEN_PARITY_N > (not). One more thing, if you have more info on the library of the part you > are targeting, you can better optimize the tree. For example, if your ASIC > library contained a 3 input XOR gate (some do) then build your tree based on > that: Eg. ODD_PARITY > Good Luck! > PJ Is it naive to think that the syntheziser will also figure this out? I mean why should it make a chain if it can make a three, and I think it should atleast be smart enough to know how to make large logic functions in 'chucks' that fit the technology --L2C --___--_-_-_-____--_-_--__---_-_--__---_-_-_-__--_---- Lasse Langwadt Christensen, MSEE (to be in 1999) Aalborg University, Department of communication tech.

Applied Signal Processing and Implementation (ASPI), mailto: phil_j.@my-dejanews.com 4/3/1999, 0:00 น. Let's take Synopsys as an example. It uses a set of rules (constraints) to synthesize. It scores each solution and uses the 'best' one.

There is a trade-off between area and speed. It typically uses the design that provides the needed speed with the smallest area.

However, for a parity function, a tree and a chain both contain the same number of gates and nets, so which is better. The tree is faster but if the chain meets your speed requirement, it MAY be used instead of the tree. What will the tool do in a given situation I can't say for sure. Not sure anyone can. I can say that I have done parity checkers and generators and Synopsys DID implement them as chains or poorly structured trees until I added the parenthesis to tell it exactly what I wanted. Would what it generated have worked?